Xilinx ise 14.7 practicals for spartan 312/1/2022

HDL Programming Lab List of Experiments Sl.

Keysight 16822A 68-Channel Portable Logic Analyzer Rohde & Schwarz Signal & Spectrum Analyzer 9 GHz Project: Design of Vending Machine using Verilog Xilinx : Simulation Cadence: 1.) Simulation 2.) Netlist, Area, Power, Timing Reports Generation 3.) Placement and Routing 4.) Post Route Simulation Synopsys: 1.) Simulation 2.) Netlist, Area, Power, Timing Reports Generation 3.) Placement and Routing 4.) Post Route Simulation Noĭesign of Mod-10 Counter using Verilog Xilinx : Simulation Cadence: 1.) Simulation 2.) Netlist, Area, Power, Timing Reports Generation 3.) Placement and Routing 4.) Post Route Simulation Synopsys: 1.) Simulation 2.) Netlist, Area, Power, Timing Reports Generation 3.) Placement and Routing 4.) Post Route Simulationĭesign of MAC Unit using Verilog Xilinx : Simulation Cadence: 1.) Simulation 2.) Netlist, Area, Power, Timing Reports Generation 3.) Placement and Routing 4.) Post Route Simulation Synopsys: 1.) Simulation 2.) Netlist, Area, Power, Timing Reports Generation 3.) Placement and Routing 4.) Post Route Simulationĭesign of Booth Multiplier using Verilog Xilinx : Simulation Cadence: 1.) Simulation 2.) Netlist, Area, Power, Timing Reports Generation 3.) Placement and Routing 4.) Post Route Simulation Synopsys: 1.) Simulation 2.) Netlist, Area, Power, Timing Reports Generation 3.) Placement and Routing 4.) Post Route Simulationĭesign of 4-tap FIR Filter using Verilog Xilinx : Simulation Cadence: 1.) Simulation 2.) Netlist, Area, Power, Timing Reports Generation 3.) Placement and Routing 4.) Post Route Simulation Synopsys: 1.) Simulation 2.) Netlist, Area, Power, Timing Reports Generation 3.) Placement and Routing 4.) Post Route Simulationĭesign of Address Generator for WiMAX Interleaver Block using Verilog Xilinx : Simulation Cadence: 1.) Simulation 2.) Netlist, Area, Power, Timing Reports Generation 3.) Placement and Routing 4.) Post Route Simulation Synopsys: 1.) Simulation 2.) Netlist, Area, Power, Timing Reports Generation 3.) Placement and Routing 4.) Post Route Simulation Verilog HDL is being used by the students to realize the problems as a circuit. The lab uses Cadence and Synopsys Tools to handle the analysis. This Lab gives an idea of Pre-Layout and Post-Layout Analysis, Synthesis, Simulation, and Layout generation to the students. The lab is supported by DeitY, New Delhi Introduction to the Laboratory This lab is also equipped with advanced equipment (Agilent 3GHz Spectrum Analyzer, Tektronix 1GHz oscilloscope, Agilent 200MHz DSO, 3GHz RF Signal generator, Mixed signal oscilloscope 350MHz, HP 100MHz oscilloscope, 68-channels Logic Analyzer, 7GHz Spectrum Analyzer and 6GHz Vector Signal Generator) and FPGA hardware kits (Xilinx Spartan 3-E/Vertex-5/Vertex-II Pro/ Vertex-7/ Xtreme DSP, Altera DE1/DE2 Cyclone II/ DSP Startix II/III, Xilinx Kintex-7/ Xilinx Zync/NET FPGA, FPGA with High-speed Analog modules, WARP V3 kit/ FMC RF-2X245 Dual Radio/USRP N210 Boards) which support for conducting the UG/PG labs and also research activities in M.S and PhD level List of PG Experiments

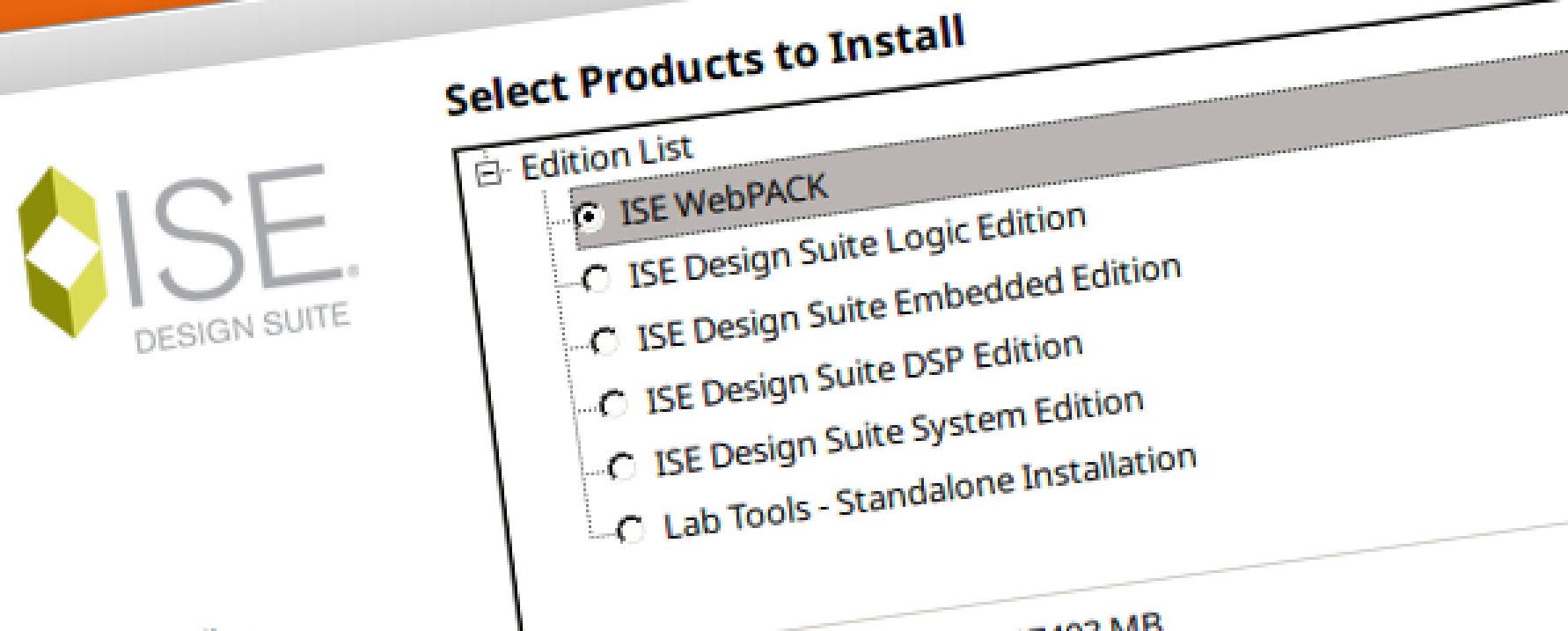

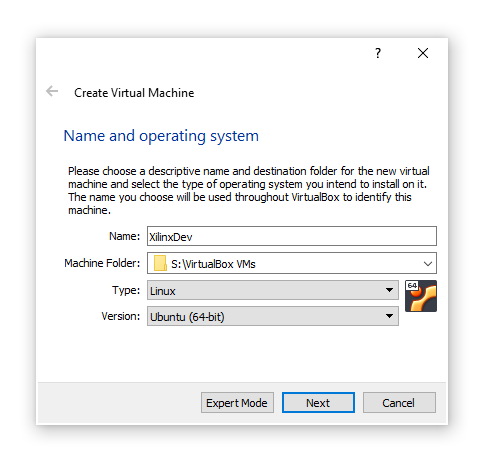

This Laboratory is equipped with Cutting-Edge Technology EDA Tools such as Cadence Virtuoso Bundle Software (IC-6.1.5) for Chip Tape-out, Mentor Graphics Calibre for DRC/LVS Validation, Synopsys for Digital IC design and validation, Cadence orCAD for PCB design, Xilinx ISE for IP-core design and validation. VLSI Labaratory Analog and Digital IC Design Laboratory

0 Comments

Leave a Reply.AuthorWrite something about yourself. No need to be fancy, just an overview. ArchivesCategories |

RSS Feed

RSS Feed